Original Harvard architecture

Source

Instruction code and data 'stored' in separate mechanisms and

accessed with dedicated circuitry.

Program and data are accessed via separated paths and

can occur at the same time (faster).

Program memory - read only during execution.

Program 'byte' and data 'byte' could be different sizes.

Separate instructions for accessing code memory and data memory.

Faster performance and lower running overhead.

Original computer architecture.

System was programmed by physically wiring the circuits to

perform desired algorithm.

Source

Instruction code and data 'stored' in separate mechanisms and

accessed with dedicated circuitry.

Program and data are accessed via separated paths and

can occur at the same time (faster).

Program memory - read only during execution.

Program 'byte' and data 'byte' could be different sizes.

Separate instructions for accessing code memory and data memory.

Faster performance and lower running overhead.

Original computer architecture.

System was programmed by physically wiring the circuits to

perform desired algorithm.

wikipedia : plugboard

Data was often provided as punched cards or some other physical

media and mechanically read.

Required manual programming and start-up.

The operator was the 'operating system'.

Difficult/impossible to re-assign resources, such as memory, between

code area and data area.

Advantage

Faster execution.

Parallel, concurrent access to code and data memory.

Disadvantage

Not able to 'borrow' unused memory from other's area.

Needs circuitry that is redundant.

wikipedia : plugboard

Data was often provided as punched cards or some other physical

media and mechanically read.

Required manual programming and start-up.

The operator was the 'operating system'.

Difficult/impossible to re-assign resources, such as memory, between

code area and data area.

Advantage

Faster execution.

Parallel, concurrent access to code and data memory.

Disadvantage

Not able to 'borrow' unused memory from other's area.

Needs circuitry that is redundant.

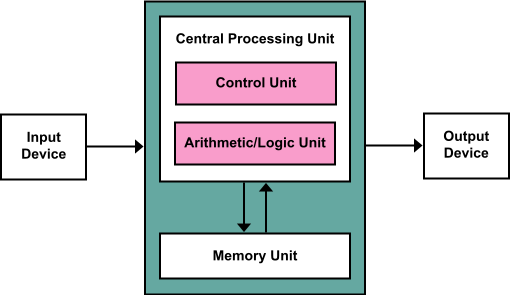

von Neumann system or stored-program architecture.

Source

Also called von Neumann architecture or stored program.

(John von Neumann, John Mauchly, J. Preser Eckert) 1940's

Both data and instructions stored in a common area. (Stored program).

Distinction between instruction and program data contextually recognized.

Instructions are sequentially read and executed using a program counter

to keep track of next instruction to be executed.

Single path for all activity.

Arbitrarily reassign resources, such as memory, between code and data

as needed.

Inexpensive hardware design, very flexible, (speed suffers).

* von Neumann bottleneck

Because both program and data access occurred over the same path,

only one of these can be happening at any moment.

Memory used to store both code and data.

Common single bus for transmission of data.

Fetch/store instruction agnostic to type of information being moved.

Advantage - optimal use of expensive memory.

Easy to redesign and implement code

Disadvantage - can access either code or data, but not both at same time.

Tends to slow execution of code.

von Neumann architecture hardware :

Processing unit.

ALU - arithmetic logic unit and work registers for holding data

and results.

Control unit holding instruction register and program counter.

Sequences through program instructions, decodes, and controls

execution of program.

I/O mechanism and interface - registers/logic for moving data and

instruction into and out of CPU.

Local memory holding both code to be executed and data to be processed

and data results.

Connected together to create an architecture called the data path.

Simple single path between memory and the computation unit of the CPU.

This is what a program "sees" when it is running.

Program execution consists of

Sequential instruction processing.

Fetch instruction from memory (addressed by instruction pointer).

Adjust instruction pointer (program counter) to next instruction.

Most modern SPUs adjust instruciton pointer concurrent with next

step.

Interpret instruction.

Execute instruction (may involve fetching/writing data from/to memory).

Repeat

Advantage - simple and flexible hardware design.

Simple internal shared bus to move instruction and data around

internally.

Same memory holds both code and data. Freedom of system to allot

needed amount at both load and run-time.

Disadvantage - von Neumann bottleneck.

Each instruction must be completed before next instruction retrieved.

Only code or only data can use internal bus or certain circuits at

a particular moment.

Other circuits may sit idle.

* Allows self-modifying code

No longer considered an advantage. Hard to debug.

Although just-in-time compilation useful.

Source

Also called von Neumann architecture or stored program.

(John von Neumann, John Mauchly, J. Preser Eckert) 1940's

Both data and instructions stored in a common area. (Stored program).

Distinction between instruction and program data contextually recognized.

Instructions are sequentially read and executed using a program counter

to keep track of next instruction to be executed.

Single path for all activity.

Arbitrarily reassign resources, such as memory, between code and data

as needed.

Inexpensive hardware design, very flexible, (speed suffers).

* von Neumann bottleneck

Because both program and data access occurred over the same path,

only one of these can be happening at any moment.

Memory used to store both code and data.

Common single bus for transmission of data.

Fetch/store instruction agnostic to type of information being moved.

Advantage - optimal use of expensive memory.

Easy to redesign and implement code

Disadvantage - can access either code or data, but not both at same time.

Tends to slow execution of code.

von Neumann architecture hardware :

Processing unit.

ALU - arithmetic logic unit and work registers for holding data

and results.

Control unit holding instruction register and program counter.

Sequences through program instructions, decodes, and controls

execution of program.

I/O mechanism and interface - registers/logic for moving data and

instruction into and out of CPU.

Local memory holding both code to be executed and data to be processed

and data results.

Connected together to create an architecture called the data path.

Simple single path between memory and the computation unit of the CPU.

This is what a program "sees" when it is running.

Program execution consists of

Sequential instruction processing.

Fetch instruction from memory (addressed by instruction pointer).

Adjust instruction pointer (program counter) to next instruction.

Most modern SPUs adjust instruciton pointer concurrent with next

step.

Interpret instruction.

Execute instruction (may involve fetching/writing data from/to memory).

Repeat

Advantage - simple and flexible hardware design.

Simple internal shared bus to move instruction and data around

internally.

Same memory holds both code and data. Freedom of system to allot

needed amount at both load and run-time.

Disadvantage - von Neumann bottleneck.

Each instruction must be completed before next instruction retrieved.

Only code or only data can use internal bus or certain circuits at

a particular moment.

Other circuits may sit idle.

* Allows self-modifying code

No longer considered an advantage. Hard to debug.

Although just-in-time compilation useful.

Most modern systems use a variety of techniques for optimizing or working around the von Neumann bottleneck. Level 1 caches on modern CPUs implemented as Harvard architecture. * Code is not modified during execution, so can be discarded when done. Micro-controllers (CPUs designed for specific tasks). Fast, economical. Inexpensive calculators are usually Harvard architecture. * Usually have limited functionality. Modified Harvard architecture. Memory closest to CPU has separate caches for code and memory. Separate internal paths for code and data. Some devices store code in flash memory addresses by separate circuits.