Back

Next

Newer 808x series CPUs.

808x - 20 bit address (1 MiB), 8/16 data bits, 5 volts.

4.7, 8 MHz.

~ 29,000 transistors

(wikipedia topic : transistor count)

12 cycles/ins.

Instruction length 1-6 bytes.

Used segmented addressing.

Capable of 1 MiB address but worked in 64KiB chunks.

Required program awareness to use all memory.

8087 co-processor for float math.

80286 - 24 bit address (16 MiB), 16 data bits, 5 volts.

4-25 MHz

~ 134,000 transistors

68 pin.

Protected memory - tasks ran in "private" space.

Could enter with software command.

To exit back to "real mode", CPU reset.

Each task assigned non-overlapping segment blocks in memory.

Segments assigned privilege levels and lower level task cannot

access higher level memory.

OS tasks assigned higher privilege.

System requires much of the memory to populated to use protected mode.

Required additional machine instructions and OS support.

Used segment register as an index to find high portion of address.

(80287 co-processor for floating point calculations)

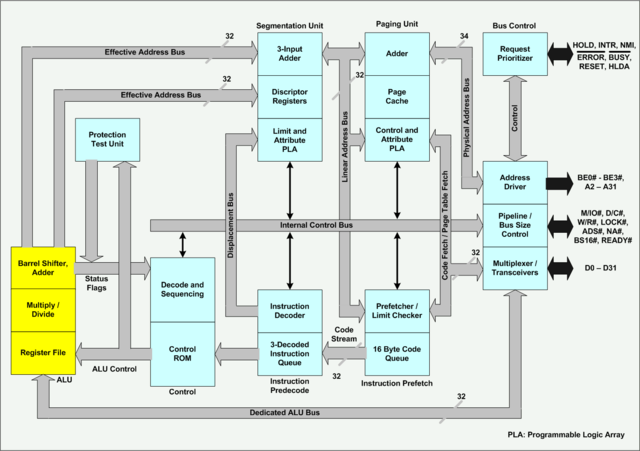

80386SX/DX - 24/32 bit address (16 MiB/4 GiB), 16 data bits, 3,5 volts.

12-40 MHz.

386SX sold as a cheaper alternative. Reduced cost of system by ~ $300-500

~ 275,000 transistors

4.5 cycles/ins.

Protected mode fixed.

Linear addressing - 4GiB address range.

Support for Virtual memory.

System to use hard drive space as a type of memory cache.

System thinks it has more primary memory that it really has.

Still produced by manufacturers other than Intel for embedded systems.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

80486 - 32 bit address, 32 data bits, 3.3/5 volts, cached.

16-100 MHz.

~ 1,180,000 transistors (math co-processor now on chip)

Mostly incremental upgrade of 80386.

Introduction of VESA (early version of dedicated video local bus).

Tightly coupled to 80486.

Pentium - 32 bit address, 64 data bits, 1.8 - 5 volts.

P5

1-2 ins./cycle average throughput(?).

~ 3,100,000 transistors

Instruction length 1-15 bytes (32 bit).

33-300MHz

Split caching.

Register renaming - dynamically tweaking instruction to use different

available register for a non-conflicting instruction.

Uses a register allocation table (RAT).

Used by/with super-scalar and vector processing.

Dual super-scalar pipelines.

U - any instruction.

V - simpler instructions.

Split level l caches, both 2-way set associative.

Superscalar dual pipeline -

one pipe able to accept any instruction.

other pipe could handle certain simple instructions.

Multi-threading - allows different tasks to abide in CPU, accessing

resources when available. Simulates a 2 CPU multi-processor.

Vector processing - applying a single instruction to an array of values.

Improved (faster) address calculations.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

80486 - 32 bit address, 32 data bits, 3.3/5 volts, cached.

16-100 MHz.

~ 1,180,000 transistors (math co-processor now on chip)

Mostly incremental upgrade of 80386.

Introduction of VESA (early version of dedicated video local bus).

Tightly coupled to 80486.

Pentium - 32 bit address, 64 data bits, 1.8 - 5 volts.

P5

1-2 ins./cycle average throughput(?).

~ 3,100,000 transistors

Instruction length 1-15 bytes (32 bit).

33-300MHz

Split caching.

Register renaming - dynamically tweaking instruction to use different

available register for a non-conflicting instruction.

Uses a register allocation table (RAT).

Used by/with super-scalar and vector processing.

Dual super-scalar pipelines.

U - any instruction.

V - simpler instructions.

Split level l caches, both 2-way set associative.

Superscalar dual pipeline -

one pipe able to accept any instruction.

other pipe could handle certain simple instructions.

Multi-threading - allows different tasks to abide in CPU, accessing

resources when available. Simulates a 2 CPU multi-processor.

Vector processing - applying a single instruction to an array of values.

Improved (faster) address calculations.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

Pentium 2 - 36 bit address (64 GiB), 64 data bits, 3.3/5 volts, cached,

233-450 MHz.

# Needs 64-bit OS to access full address range.

# Most systems still come with a max of 4GiB of memory.

7,500,000 transistors

Pentium 3 - 36 bit address, 64 data bits, 1.65-2 volts, cached, 450-1400 MHz.

9,500,000 transistors

Pentium 4 - 1.3-3.6 GHz.

42,000,000 transistors (part from larger on-board caching)

Pentium D - 31 stage pipeline.

Very high power consumption.

Pentium M - 14 stage pipeline. Register naming and register file (ALU).

Notice more stages make individual actions simpler but slow the overall

progress of an instruction.

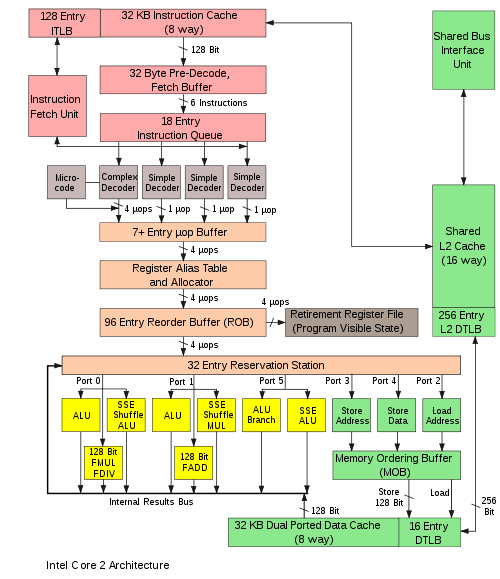

Pentium Dual-core (2007) - 1.6-1.8 GHz. wider super-scale on each core.

2 or more actual CPU cores with their own split level 1 caches.

Core 2 Duo ~ 291,000,000 transistors

Six core I7 ~ 1,170,000,000

Shorter but wider pipeline means CPU can run at lower clock speed (less

power draw) and still be faster overall.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

Pentium 2 - 36 bit address (64 GiB), 64 data bits, 3.3/5 volts, cached,

233-450 MHz.

# Needs 64-bit OS to access full address range.

# Most systems still come with a max of 4GiB of memory.

7,500,000 transistors

Pentium 3 - 36 bit address, 64 data bits, 1.65-2 volts, cached, 450-1400 MHz.

9,500,000 transistors

Pentium 4 - 1.3-3.6 GHz.

42,000,000 transistors (part from larger on-board caching)

Pentium D - 31 stage pipeline.

Very high power consumption.

Pentium M - 14 stage pipeline. Register naming and register file (ALU).

Notice more stages make individual actions simpler but slow the overall

progress of an instruction.

Pentium Dual-core (2007) - 1.6-1.8 GHz. wider super-scale on each core.

2 or more actual CPU cores with their own split level 1 caches.

Core 2 Duo ~ 291,000,000 transistors

Six core I7 ~ 1,170,000,000

Shorter but wider pipeline means CPU can run at lower clock speed (less

power draw) and still be faster overall.

source : https://en.wikipedia.org/wiki/Intel_Core_(microarchitecture)

Itanium 2 - 44 bit address, 128 data bits, 1.65-2 volts, cached.

High speed RISC architecture. Not legacy compatible with the 80x86

architecture.

3 or more ins./cycle. servers - moving data rather than calculating.

Windows, Linux, Solaris, etc. available.

In addition :

General purpose registers were also extended to handle the wider data

bus (same basic instructions - additional addressing modes).

Register files allowing context switching by switching pointers to

working general purpose registers rather than storing.

source : https://en.wikipedia.org/wiki/Intel_Core_(microarchitecture)

Itanium 2 - 44 bit address, 128 data bits, 1.65-2 volts, cached.

High speed RISC architecture. Not legacy compatible with the 80x86

architecture.

3 or more ins./cycle. servers - moving data rather than calculating.

Windows, Linux, Solaris, etc. available.

In addition :

General purpose registers were also extended to handle the wider data

bus (same basic instructions - additional addressing modes).

Register files allowing context switching by switching pointers to

working general purpose registers rather than storing.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

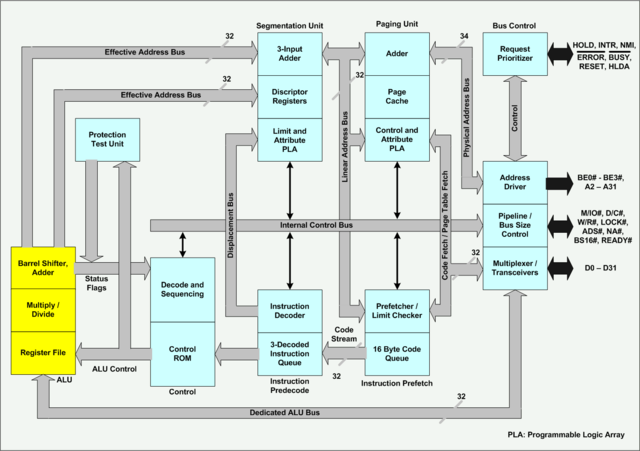

80486 - 32 bit address, 32 data bits, 3.3/5 volts, cached.

16-100 MHz.

~ 1,180,000 transistors (math co-processor now on chip)

Mostly incremental upgrade of 80386.

Introduction of VESA (early version of dedicated video local bus).

Tightly coupled to 80486.

Pentium - 32 bit address, 64 data bits, 1.8 - 5 volts.

P5

1-2 ins./cycle average throughput(?).

~ 3,100,000 transistors

Instruction length 1-15 bytes (32 bit).

33-300MHz

Split caching.

Register renaming - dynamically tweaking instruction to use different

available register for a non-conflicting instruction.

Uses a register allocation table (RAT).

Used by/with super-scalar and vector processing.

Dual super-scalar pipelines.

U - any instruction.

V - simpler instructions.

Split level l caches, both 2-way set associative.

Superscalar dual pipeline -

one pipe able to accept any instruction.

other pipe could handle certain simple instructions.

Multi-threading - allows different tasks to abide in CPU, accessing

resources when available. Simulates a 2 CPU multi-processor.

Vector processing - applying a single instruction to an array of values.

Improved (faster) address calculations.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

80486 - 32 bit address, 32 data bits, 3.3/5 volts, cached.

16-100 MHz.

~ 1,180,000 transistors (math co-processor now on chip)

Mostly incremental upgrade of 80386.

Introduction of VESA (early version of dedicated video local bus).

Tightly coupled to 80486.

Pentium - 32 bit address, 64 data bits, 1.8 - 5 volts.

P5

1-2 ins./cycle average throughput(?).

~ 3,100,000 transistors

Instruction length 1-15 bytes (32 bit).

33-300MHz

Split caching.

Register renaming - dynamically tweaking instruction to use different

available register for a non-conflicting instruction.

Uses a register allocation table (RAT).

Used by/with super-scalar and vector processing.

Dual super-scalar pipelines.

U - any instruction.

V - simpler instructions.

Split level l caches, both 2-way set associative.

Superscalar dual pipeline -

one pipe able to accept any instruction.

other pipe could handle certain simple instructions.

Multi-threading - allows different tasks to abide in CPU, accessing

resources when available. Simulates a 2 CPU multi-processor.

Vector processing - applying a single instruction to an array of values.

Improved (faster) address calculations.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

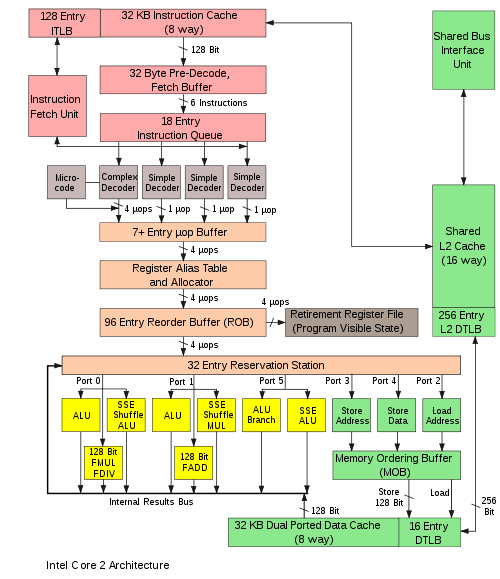

Pentium 2 - 36 bit address (64 GiB), 64 data bits, 3.3/5 volts, cached,

233-450 MHz.

# Needs 64-bit OS to access full address range.

# Most systems still come with a max of 4GiB of memory.

7,500,000 transistors

Pentium 3 - 36 bit address, 64 data bits, 1.65-2 volts, cached, 450-1400 MHz.

9,500,000 transistors

Pentium 4 - 1.3-3.6 GHz.

42,000,000 transistors (part from larger on-board caching)

Pentium D - 31 stage pipeline.

Very high power consumption.

Pentium M - 14 stage pipeline. Register naming and register file (ALU).

Notice more stages make individual actions simpler but slow the overall

progress of an instruction.

Pentium Dual-core (2007) - 1.6-1.8 GHz. wider super-scale on each core.

2 or more actual CPU cores with their own split level 1 caches.

Core 2 Duo ~ 291,000,000 transistors

Six core I7 ~ 1,170,000,000

Shorter but wider pipeline means CPU can run at lower clock speed (less

power draw) and still be faster overall.

CC BY-SA 3.0, https://commons.wikimedia.org/w/index.php?curid=425200

Pentium 2 - 36 bit address (64 GiB), 64 data bits, 3.3/5 volts, cached,

233-450 MHz.

# Needs 64-bit OS to access full address range.

# Most systems still come with a max of 4GiB of memory.

7,500,000 transistors

Pentium 3 - 36 bit address, 64 data bits, 1.65-2 volts, cached, 450-1400 MHz.

9,500,000 transistors

Pentium 4 - 1.3-3.6 GHz.

42,000,000 transistors (part from larger on-board caching)

Pentium D - 31 stage pipeline.

Very high power consumption.

Pentium M - 14 stage pipeline. Register naming and register file (ALU).

Notice more stages make individual actions simpler but slow the overall

progress of an instruction.

Pentium Dual-core (2007) - 1.6-1.8 GHz. wider super-scale on each core.

2 or more actual CPU cores with their own split level 1 caches.

Core 2 Duo ~ 291,000,000 transistors

Six core I7 ~ 1,170,000,000

Shorter but wider pipeline means CPU can run at lower clock speed (less

power draw) and still be faster overall.

source : https://en.wikipedia.org/wiki/Intel_Core_(microarchitecture)

Itanium 2 - 44 bit address, 128 data bits, 1.65-2 volts, cached.

High speed RISC architecture. Not legacy compatible with the 80x86

architecture.

3 or more ins./cycle. servers - moving data rather than calculating.

Windows, Linux, Solaris, etc. available.

In addition :

General purpose registers were also extended to handle the wider data

bus (same basic instructions - additional addressing modes).

Register files allowing context switching by switching pointers to

working general purpose registers rather than storing.

source : https://en.wikipedia.org/wiki/Intel_Core_(microarchitecture)

Itanium 2 - 44 bit address, 128 data bits, 1.65-2 volts, cached.

High speed RISC architecture. Not legacy compatible with the 80x86

architecture.

3 or more ins./cycle. servers - moving data rather than calculating.

Windows, Linux, Solaris, etc. available.

In addition :

General purpose registers were also extended to handle the wider data

bus (same basic instructions - additional addressing modes).

Register files allowing context switching by switching pointers to

working general purpose registers rather than storing.