Back

Next

Formatting or representing data for transmission and storage.

Check out Line code

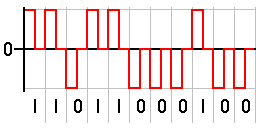

Technique : RZ - return to zero.

Provides a neutral non-transmitting condition.

Tristate logic possible example.

Used where logic circuits function asynchronously

- non-continuous interaction.

More commonly implemented on top of a carrier signal such as

Pulse amplitude modulation ATSC (digital TV)

Frequency modulation

Phase shift modulation.

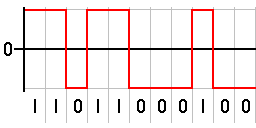

Technique : NRZ - non-return to zero.

Ones at one level and zeros at another.

Does not support a neutral (non-data) level.

Provides a neutral non-transmitting condition.

Tristate logic possible example.

Used where logic circuits function asynchronously

- non-continuous interaction.

More commonly implemented on top of a carrier signal such as

Pulse amplitude modulation ATSC (digital TV)

Frequency modulation

Phase shift modulation.

Technique : NRZ - non-return to zero.

Ones at one level and zeros at another.

Does not support a neutral (non-data) level.

Highest data density transferal.

System bus.

Two forms

Standard NRZ (0 is one voltage level, 1 is its inverse) +/-5 volts.

Unipolar

Charged voltage is a 1,

0 volts is a zero.

Simple to implement but power flows in one direction (DC bias) requiring a return path.

Used in early TTL logic but modern systems avoid DC biasing.

Problem :

Really long strings of all 1s or 0s loose distinction.

Level based signals can be inverted (zeros confused with ones)

Accumulated charge - if signal is electric and there is a long string

of a particular bit value, unbalanced electrical charges accumulate

at one end of the communication.

This is sometimes called the DC component.

Required a shared ground between sender and receiver.

Requires DC coupling.

Possible Solutions:

Assume sender and receiver synchronized.

Use very precise clocks and equipment.

Used with short-reach fiber optics. (?)

Provide second track or signal giving a timing measure.

Computer bus with clock line.

Use occasional re-sync signal (reserved bit sequence)

Non-DSL modems use a logical form of this.

Transfer 7 or 8 bits of data at a time enclosed in start and stop bits.

High overhead but inexpensive technology.

Use an encoding scheme to limit the number or run of consecutive zeros

or ones.

RLL - run length limited.

Encodes set of bits on a larger bit set providing guaranteed transitions

with in a small time period.

Choose complimentary voltage levels, +5 for 1, -5 for 0.

Helps attenuate accumulated power transferal

but doesn't guarentee it.

These solutions require more resources or expense.

Next

Highest data density transferal.

System bus.

Two forms

Standard NRZ (0 is one voltage level, 1 is its inverse) +/-5 volts.

Unipolar

Charged voltage is a 1,

0 volts is a zero.

Simple to implement but power flows in one direction (DC bias) requiring a return path.

Used in early TTL logic but modern systems avoid DC biasing.

Problem :

Really long strings of all 1s or 0s loose distinction.

Level based signals can be inverted (zeros confused with ones)

Accumulated charge - if signal is electric and there is a long string

of a particular bit value, unbalanced electrical charges accumulate

at one end of the communication.

This is sometimes called the DC component.

Required a shared ground between sender and receiver.

Requires DC coupling.

Possible Solutions:

Assume sender and receiver synchronized.

Use very precise clocks and equipment.

Used with short-reach fiber optics. (?)

Provide second track or signal giving a timing measure.

Computer bus with clock line.

Use occasional re-sync signal (reserved bit sequence)

Non-DSL modems use a logical form of this.

Transfer 7 or 8 bits of data at a time enclosed in start and stop bits.

High overhead but inexpensive technology.

Use an encoding scheme to limit the number or run of consecutive zeros

or ones.

RLL - run length limited.

Encodes set of bits on a larger bit set providing guaranteed transitions

with in a small time period.

Choose complimentary voltage levels, +5 for 1, -5 for 0.

Helps attenuate accumulated power transferal

but doesn't guarentee it.

These solutions require more resources or expense.

Next

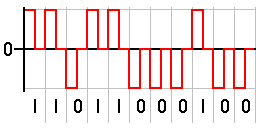

Provides a neutral non-transmitting condition.

Tristate logic possible example.

Used where logic circuits function asynchronously

- non-continuous interaction.

More commonly implemented on top of a carrier signal such as

Pulse amplitude modulation ATSC (digital TV)

Frequency modulation

Phase shift modulation.

Technique : NRZ - non-return to zero.

Ones at one level and zeros at another.

Does not support a neutral (non-data) level.

Provides a neutral non-transmitting condition.

Tristate logic possible example.

Used where logic circuits function asynchronously

- non-continuous interaction.

More commonly implemented on top of a carrier signal such as

Pulse amplitude modulation ATSC (digital TV)

Frequency modulation

Phase shift modulation.

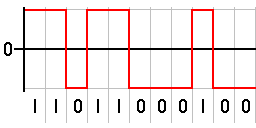

Technique : NRZ - non-return to zero.

Ones at one level and zeros at another.

Does not support a neutral (non-data) level.

Highest data density transferal.

System bus.

Two forms

Standard NRZ (0 is one voltage level, 1 is its inverse) +/-5 volts.

Unipolar

Charged voltage is a 1,

0 volts is a zero.

Simple to implement but power flows in one direction (DC bias) requiring a return path.

Used in early TTL logic but modern systems avoid DC biasing.

Problem :

Really long strings of all 1s or 0s loose distinction.

Level based signals can be inverted (zeros confused with ones)

Accumulated charge - if signal is electric and there is a long string

of a particular bit value, unbalanced electrical charges accumulate

at one end of the communication.

This is sometimes called the DC component.

Required a shared ground between sender and receiver.

Requires DC coupling.

Possible Solutions:

Assume sender and receiver synchronized.

Use very precise clocks and equipment.

Used with short-reach fiber optics. (?)

Provide second track or signal giving a timing measure.

Computer bus with clock line.

Use occasional re-sync signal (reserved bit sequence)

Non-DSL modems use a logical form of this.

Transfer 7 or 8 bits of data at a time enclosed in start and stop bits.

High overhead but inexpensive technology.

Use an encoding scheme to limit the number or run of consecutive zeros

or ones.

RLL - run length limited.

Encodes set of bits on a larger bit set providing guaranteed transitions

with in a small time period.

Choose complimentary voltage levels, +5 for 1, -5 for 0.

Helps attenuate accumulated power transferal

but doesn't guarentee it.

These solutions require more resources or expense.

Next

Highest data density transferal.

System bus.

Two forms

Standard NRZ (0 is one voltage level, 1 is its inverse) +/-5 volts.

Unipolar

Charged voltage is a 1,

0 volts is a zero.

Simple to implement but power flows in one direction (DC bias) requiring a return path.

Used in early TTL logic but modern systems avoid DC biasing.

Problem :

Really long strings of all 1s or 0s loose distinction.

Level based signals can be inverted (zeros confused with ones)

Accumulated charge - if signal is electric and there is a long string

of a particular bit value, unbalanced electrical charges accumulate

at one end of the communication.

This is sometimes called the DC component.

Required a shared ground between sender and receiver.

Requires DC coupling.

Possible Solutions:

Assume sender and receiver synchronized.

Use very precise clocks and equipment.

Used with short-reach fiber optics. (?)

Provide second track or signal giving a timing measure.

Computer bus with clock line.

Use occasional re-sync signal (reserved bit sequence)

Non-DSL modems use a logical form of this.

Transfer 7 or 8 bits of data at a time enclosed in start and stop bits.

High overhead but inexpensive technology.

Use an encoding scheme to limit the number or run of consecutive zeros

or ones.

RLL - run length limited.

Encodes set of bits on a larger bit set providing guaranteed transitions

with in a small time period.

Choose complimentary voltage levels, +5 for 1, -5 for 0.

Helps attenuate accumulated power transferal

but doesn't guarentee it.

These solutions require more resources or expense.

Next