Robert Rannie Milica Kozomara Northern Illinois University - DeKalb, IL Texas Instruments - Dallas,TX

# Mainframe Operating Systems "Boot Camp"

FLIH: I/O INTERRUPTS

Part 5

Session #2899 SHARE 112 in Austin, March 2009

# Our Agenda for the Week

- #2895 Part I: The General Purpose Computer and Interrupts

- #2896 Part 2: From IPL to Running Programs

- #2897 Part 3: SVCs and More SVCs

- #2898 Part 4: Program Interrupts (You Want An Exit With That?)

- <u>#2899 Part 5: FLIH: I/O INTERRUPTS</u>

- #2894 Mainframe Operating System Boot Camp: Highlights

"Tell 'em what you're gonna tell 'em"

- Dispatch Priority + Wait TCB's Role

- The I/O Concept

- Programs Execute CPU Instructions

- For I/O: New Control Blocks (CB)

- To Start I/O: New Procedures

- I/O Interrupt Processing I/O FLIH

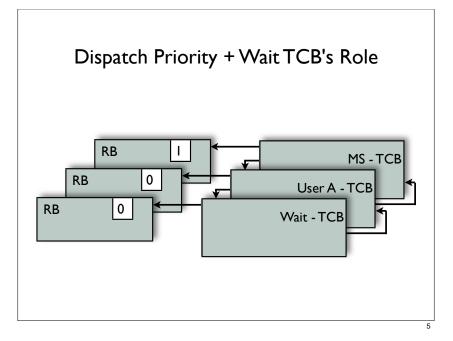

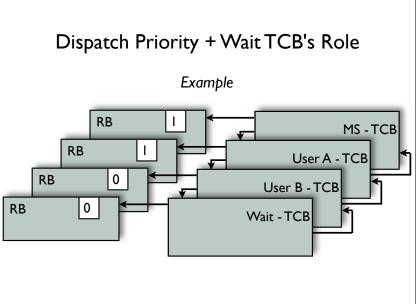

## Dispatch Priority + Wait TCB's Role

- Recall:

- TCB/RB chain and RBWCF when user job is running

- Master Scheduler (MS) called SVC I to make itself Non-Diapatchable: RBWCF=I

- The Dispatcher "Dispatched" the next TCB/RB in the chain (Job A)

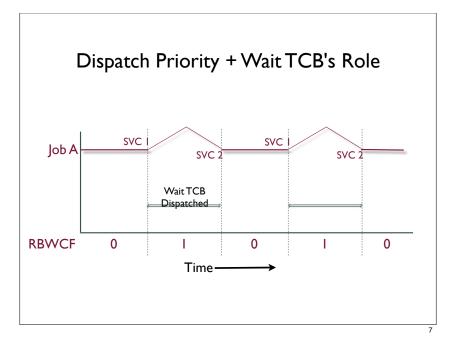

Job A is now running and wants to do I/O

- To do I/O:

- Job A issues SVC 0

- SVC 0 issues SVC 1 on behalf of Job A: Job A is made non Dispatchable

- After I/O op, IO-FLIH issues SVC 2 on behalf of Job A: Job A is Dispatchable again

- Wait TCB/RB :

- always dispatchable!

- dispatched when there are no other TCB/ RBs

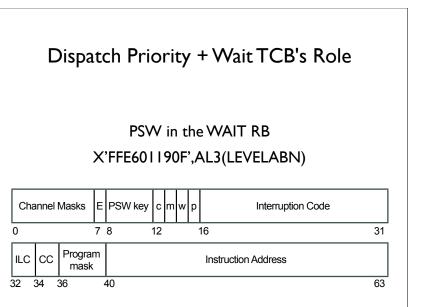

- Wait Bit set to I = Don't Run (i.e. "wait")

Dispatch Priority + Wait TCB's Role

- For the state of the CPU to be changed from Wait, it is necessary for an Interrupt to occur that replaces the current PSW with one in which the Wait Bit = 0

- Optimization will minimize the amount of "Waiting" time

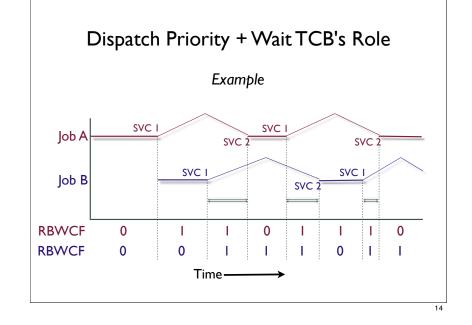

#### Dispatch Priority + Wait TCB's Role

Example

- Consider Job B in TCB/RB chain below Job A and above Wait

- When Job A starts its I/O, Job B is dispatched

9

Example

- Suppose Job B does an I/O by issuing an SVC 0

- SVC 0 issues an SVC I on behalf of Job B

- Job B is now non-dispatchable

- After I/O operation, IO-FLIH issues SVC 2 on behalf of Job B

- Now Job B is dispatchable again

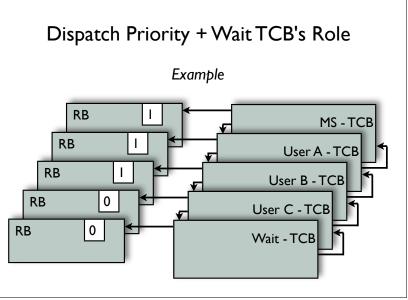

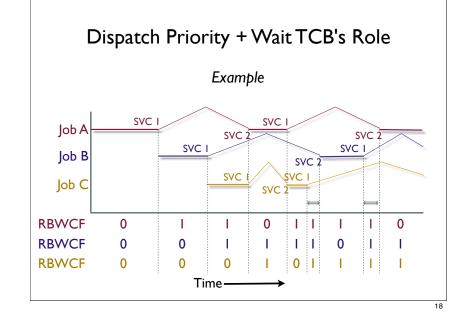

## Dispatch Priority + Wait TCB's Role

#### Example

- Consider Job C in TCB/RB chain below Job B and above Wait

- When Job B starts its I/O, Job C is dispatched

Example

- Suppose Job C does an I/O by issuing an SVC 0

- SVC 0 issues an SVC I on behalf of Job C

- Job C is now non-dispatchable

- After I/O operation, IO-FLIH issues SVC 2 on behalf of Job C

- Now Job C is dispatchable again

## The I/O Concept

Three Steps, and Consideration

- I/O will be Started by the CPU

- Once Started, I/O is Controlled and Processed by the Channel

- Interrupt(s) Signaling Completion are processed by I/O-FLIH

- Should the problem program be allowed to execute while I/O is being done on its behalf?

#### I/O will be Started by the CPU

- User may request I/O by issuing SVC 0

- SVC 0 will issue SVC I on behalf of the user

- User program is non-dispatchable until I/O has completed

- Before issuing the CPU instruction to start the CP store A( 1st CCW of CP ) in Channel Address Word (CAW)

- CAW is located in low core at X'48'

## The I/O Concept

I/O will be Started by the CPU

- The hardware address of the specified device must be known

- Device Addresses are given in a two byte form

## Channel Address A(CU) A(device)

- Up to 16 Devices may be attached to one Control Unit (CU)

- Up to 16 CU may be attached to one Channel

## The I/O Concept

I/O will be Started by the CPU

- The Start I/O (SIO) instruction

- issued by the CPU to direct the CP to take over I/O

- specifies the Device Address to be involved in I/O

- is a privileged instruction

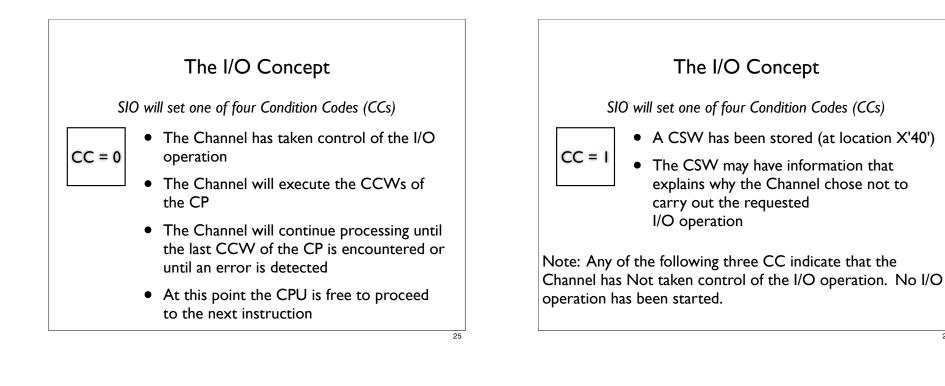

- will set one of four Condition Codes (CCs)

## The I/O Concept

I/O will be Started by the CPU

- The Start I/O (SIO) instruction

- the original IBM sys/360/370 I/O initiating instruction

- used in SOS/Assist-v

- replaced by Start Subchannel (SSCH) in MVS/zOS

#### The I/O Concept

I/O will be Started by the CPU

- Prior to issuing the SIO instruction

- obtain the hardware address (Channel, Control Unit, Device) and make it available to SIO

- build the CP in processor memory

- store A(1st CCW of CP) in the CAW (at X'48')

21

## The I/O Concept

SIO will set one of four Condition Codes (CCs)

Note: In the SOS, any CC other than zero calls for termination of the program and determination of the error cause.

The possible exception to this practice might be when CC=I with the Unit Exception bit set to I in the CSW indicating End of File (EOF).

# The I/O Concept

Started I/O is Controlled and Processed by the Channel

- I/O is started by the CPU and carried out by the channel

- Channel has instructions called Channel Command Words (CCWs)

- Each CCW

- is eight bytes in length

- must reside on a double word boundary

- must reside in processor memory

## The I/O Concept

Started I/O is Controlled and Processed by the Channel

• A Channel Program (CP) typically consists of a number of CCWs located in succession in ascending memory locations

#### The I/O Concept

Started I/O is Controlled and Processed by the Channel

- CCWs that comprise the CP

- are mostly contiguous

- are capable of conditional branching

- contain flags that instruct CP to (among other things) continue to the next CCW and execute it or to stop

- When a CP stops an appropriate I/O Interrupt is sent to the CPU by the channel

29

## The I/O Concept

Interrupt(s) Signaling Completion are processed by I/O-FLIH

- I/O FLIH performs the same 'good stuff' as all FLIHs

- The I/O FLIH chooses further actions based on

- the stored CSW (X'40')

- the UCB for the device involved

- the RQE for this specific operation

- the I/O Old PSW

## Programs Execute CPU Instructions

Sequential and Partitioned Access Methods

- The 'SPAM' assignment

- usually carried out entirely in MVS/zOS

- uses Queued and Basic AMs

- implements Buffering and Blocking concepts

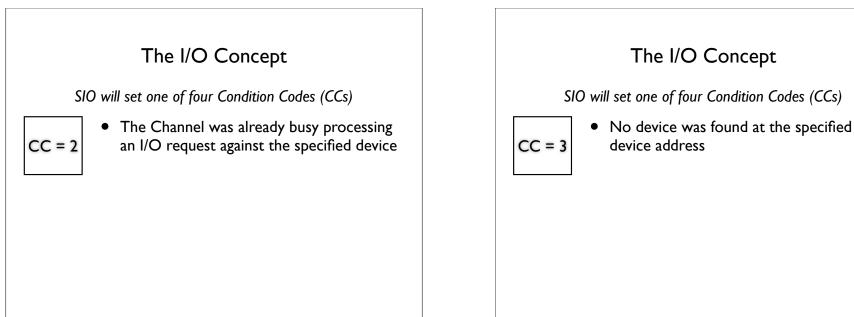

For I/O: New Control Blocks (CB)

- A Unit Control Block (UCB) is provided in the processor's Fixed Storage for EACH I/O device

- One Request Queue Element (RQE) residing in a dynamic storage block is connected to the UCB for each I/O request initiated to that specific device

- This in the case in both a uni-programming and a multi-programming environment

# For I/O: New Control Blocks (CB)

#### • Use the 'UCB' DSECT to identify fields of the UCB

| UCB      | DSECT |                                                    |

|----------|-------|----------------------------------------------------|

| UCBIDENT | DS    | CL3'UCB',X'FF' DOCUMENTATION                       |

| UCBCHAN  | DS    | X'0000' DEVICE ADDRESS IN HEX                      |

| UCBFLA   | DS    | X'00' = FREE, X'FF' = BUSY                         |

| UCBFLB   | DS    | X'00' RESERVED                                     |

| UCBUCB   | DS    | A(0) ADD. NEXT UCB ON CHAIN OR 0 IF THIS = LAST    |

| UCBNAME  | DS    | CL4'NAME' DEVICE ADDRESS IN EBCDIC                 |

| UCBCURQE | DS    | A(0) ADDRESS OF RQE CURRENTLY BEING PROCESSED      |

| UCBWARQE | DS    | A(0) ADD. FIRST RQE IN WAIT QUEUE,/0 IF NONE THERE |

| UCBIOSTR | DS    | A(0) ADDRESS OF DEVICE'S I/O START ROUTINE         |

|          | DS    | A(0) RESERVED                                      |

| UCBLNTH  | EQU   | * - UCBIDENT LENGTH OF UCB (X'20')                 |

|          | •     |                                                    |

33

| FO                 | r I/C | D: New Control Blocks (CB)                                                   |

|--------------------|-------|------------------------------------------------------------------------------|

| • Us               | e the | e 'RQE' DSECT to identify fields of the                                      |

| RÇ                 | )E    |                                                                              |

| RQE                | DSECT |                                                                              |

| RQEIDENT<br>RQEIOB |       | CL4'RQE ' DOCUMENTATION                                                      |

| RQEICB             |       | A(0) ADDRESS OF IOB THAT GENERATED THIS RQE<br>A(0) ADD. OF UCB WHEN IN USE. |

| QETCB              |       | A(0) ADD. OF USERS TCB                                                       |

| •                  |       | A(0) ADD. OF RB IN TCB ISSUING I/O REQUEST                                   |

|                    |       | A(0) ADD NEXT RQE IN UCB WAIT QUE./0 IF THIS=LAST                            |

| RQEIOECB           | DS    | A(0) ECB FOR WAIT/POST OF THIS RQE V6.10                                     |

|                    | DS    | A(0) RESERVED V6.10                                                          |

| RQELNTH            | EQU   | *-RQE LENGTH OF RQE (X'20')                                                  |

|                    |       |                                                                              |

|                    |       |                                                                              |

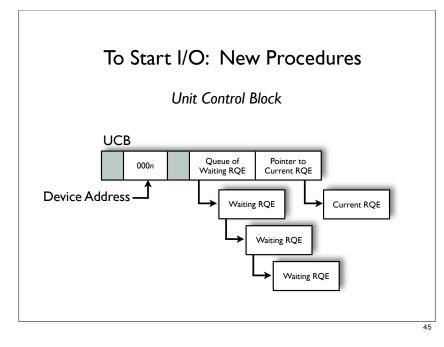

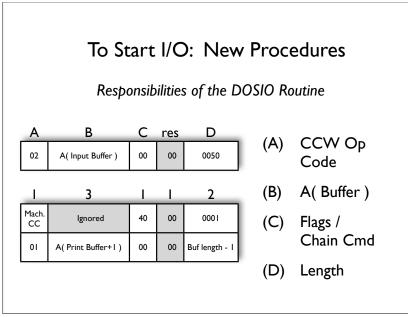

#### To Start I/O: New Procedures

• The world of 'Real I/O' in the Assist-V simulator environment has four Unit Record devices

| r                         |                    |  |

|---------------------------|--------------------|--|

| 'Real I/O' Device Address |                    |  |

| X'000C'                   | Card Reader        |  |

| X'000D'                   | Card Reader        |  |

| X,000E,                   | Printer            |  |

| X'000F'                   | Printer            |  |

|                           | X'000C'<br>X'000D' |  |

To Start I/O: New Procedures

- Assist-V has located these Unit Record devices on Channel 0

- The simulator can also support DASD devices on Channels I & 2

### To Start I/O: New Procedures

- To begin 'Real I/O' (in SOS)

- point RI to an I/O block with non-zero IOBDEVAD field containing the address of a Unit Record device

- call SVC 0

- In this case SVC 0 will

- not use XREAD and XPRNT commands

- BR R12 to the 1st Start I/O Routine

## To Start I/O: New Procedures

- Start I/O Routines

- RQE Enqueue

- BEGINIO

- DO-SIO

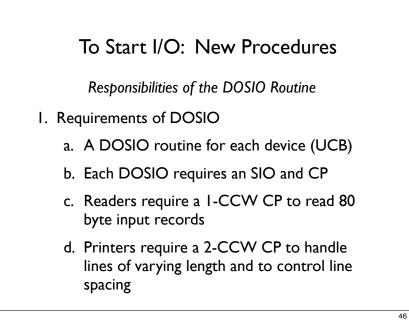

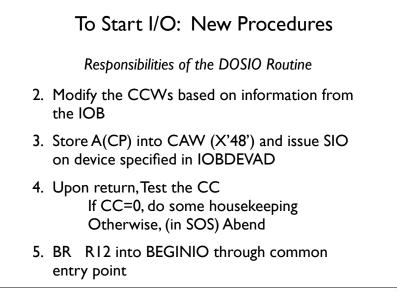

### To Start I/O: New Procedures

Responsibilities of the RQE Enqueue Routine

- I. Obtain an RQE from Dynamic Storage

- Clear it to X'00' and fill required fields

- Add it to the end of the RQE Queue attached at the UCBWARQE field of the UCB belonging to the device designated in the IOBDEVAD field of the IOB

- 2. BR entry/exit SVC I

- 3. BR R12 to the BEGINIO Routine

#### To Start I/O: New Procedures

Responsibilities of the BEGINIO Routine

- I. Search the UCB chain for the 1st UCB that meets these criteria

- a. The device is NOT-busy

- b. The UCBWARQE field is not zero

If no such UCBs are found, exit BEGINIO via R12 to Chap/Dispatcher

## To Start I/O: New Procedures

Responsibilities of the BEGINIO Routine

- 2. Dequeue first RQE from UCBWARQE

- 3. Point UCBCURQE field to dequeued RQE.

- 4. BR R12 to this UCB's DOSIO Routine

The DOSIO Routine will perform the set up necessary to issue an SIO

41

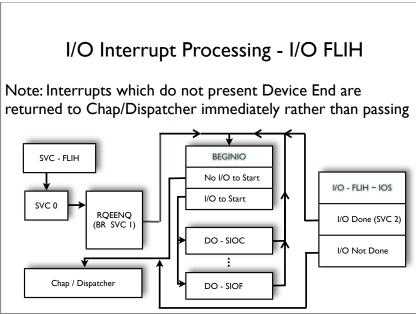

## I/O Interrupt Processing - I/O FLIH

- Recall:

- I/O FLIH performs same 'good stuff' as all FLIH

- Then examines the stored CSW

- The examination is the first of multiple steps to determine the state of the just-completed I/ O operation

## I/O Interrupt Processing - I/O FLIH

#### The Examination of the CSW

- Test Unit and Channel Status bits (32-39,40-47) for 'Bad' bits

- 'Bad' bits present? Terminate the program

- 'Bad' bits are ANY enabled bits other than Channel End Control Unit End Device End Incorrect Length Unt Exception

## I/O Interrupt Processing - I/O FLIH

The Examination of the CSW

- There are three possible 'end-generating interrupts'

- Channel end

- Control Unit end

- Device end

- Receiving multiple 'ends' is OK

- DEVICE END is required it proves completion of the operation

## I/O Interrupt Processing - I/O FLIH

Examine the I/O Old PSW

- Get A( device ) from I/O Old PSW interrupt code field

- Use device address to find proper UCB & current RQE

- Use the current RQE field, RQEIOECB, with a Post Code of X'7F',C'IOS' (indicating the 'I/O Supervisor')

- BR entry & exit SVC 2 to make the program that requested the I/O dispatchable

49

## I/O Interrupt Processing - I/O FLIH

Examine the I/O Old PSW

- Free the CB memory used for the RQE (& return to stack)

- Following Interrupt Processing in the IO-FLIH, exit to the common entry point of BEGINIO.

- BEGINIO can now start any enqueued I/O requests

- If there are no more I/O requests to start, BEGINIO goes to Chap/Dispatcher

## I/O Interrupt Processing - I/O FLIH

A Note on SOS and Chap

- Only some of the SOS assignments have been done with Chap

- It is an SVC that may change priority of TCBs

- Accumulated accounting information may be used to decide where in the TCB chain a particular job (TCB) should be located

- If Chap is active it may change the position (and thereby the priority) of a TCB and then enter the Dispatcher

53