Robert Rannie Milica Kozomara Northern Illinois University - DeKalb, IL Texas Instruments - Dallas,TX

# Mainframe Operating Systems "Boot Camp"

From IPL to Running Programs

Part 2

Session #2896 SHARE 112 in Austin, March 2009

#### Our Agenda for the Week

- #2895 Part I: The General Purpose Computer and Interrupts

- <u>#2896 Part 2: From IPL to Running Programs</u>

- #2897 Part 3: SVCs and More SVCs

- #2898 Part 4: Program Interrupts (You Want An Exit With That?)

- #2899 Part 5: FLIH: I/O INTERRUPTS

- #2894 Mainframe Operating System Boot Camp: Highlights

"Tell 'em what you're gonna tell 'em"

- What you need to RUN a program

- The Initial Program Load (IPL)

- The Dispatcher

- SVC First Level Interrupt Handlers (FLIHs)

- The Master Scheduler

#### What you Need to RUN a Program

Just a Few Good Routines and Control Blocks (CBs)

- Initial Program Load (IPL)

- Dispatching

- SVC FLIH

- SVC 8 (Loader)

- SVC I (Wait)

- Master Scheduler

### What you Need to RUN a Program

Set up the Following Routines and CBs

- PSA ("Low Core")

- The CVT (Memory label = 'MYCVT')

- Other Routines & CBs (in SOS-A)

- Dynamic memory area stack (CB100s), Size X'100'

- TCBs & RBs (In dynamic memory areas

### What you Need to RUN a Program

#### **Required Initialization**

|       | IPL PSW         | X'18' | External Old                  | PSW        | 1   |       |                         |

|-------|-----------------|-------|-------------------------------|------------|-----|-------|-------------------------|

| X'0'  | Restart New PSW | X'20' | X'20' Supervisor Call Old PSW |            |     |       |                         |

| X'8'  | IPL CCWI        | X'28' | Program Che                   | ck Old PSW |     |       |                         |

|       | Restart Old PSW | X'30' |                               |            | łг  | X'58' | External New PSW        |

| X'10' | IPL CCW2        |       |                               |            | ┥┝  |       | External New F3VV       |

| ~ 10  | A(MYCVT)        | X'38' | Input/Output Old PSW          |            | L   | X'60' | Supervisor Call New PSW |

|       |                 | X'40' | Channel Statu                 | is Word    |     | X'68' | Program Check New PSW   |

|       |                 | X'48' | CAW                           | A(MYCVT)   | 1 [ | X'70' | Machine Check New PSW   |

|       |                 | X'50' | CLOCK                         | Trace Info | 1 [ | X'78' | Input/Output New PSW    |

- Four 64 byte save areas One for each, EX, SV, PC, and IO

- 4 F'0' at 'TCBWORDS' DSECT is IEATCBP

#### What you Need to RUN a Program

Typical Locations

- X'1200' MYCVT

- X'I 300' SVC TABLE

- X'1800' Dispatcher

- X'I C00' IPL Program

- X'2000' 5 FLIH (One for each Interrupt type)

#### What you Need to RUN a Program

#### Typical Locations

- X'6000' Location for SVC Modules

- SVCs 1, 3, and 8 in Instructor Supplied Macro Library: 'WAITS', 'EXIT' & 'LOADERX'

- X'E200' Master Scheduler (MS)

- X'F000' Pool of CB100s

5

#### What you Need to RUN a Program

**IPL Program**

- The IPL process consists of

- I/O Phase loads OS into memory

- PSW Loading Phase load current PSW

- At this point it as if you are at the top of the BIF loop

#### What you Need to RUN a Program

3 Ways to a New Current PSW

- Via an Interrupt

- Via Load PSW Instruction (LPSW)

- Via Initial Program Load (IPL) process

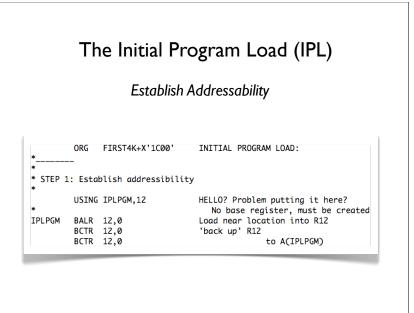

# The Initial Program Load (IPL)

| * |          |                                                                   | I |

|---|----------|-------------------------------------------------------------------|---|

| * | STEP 1 : | Establish addressibility                                          | Ρ |

| * | STEP 2 : | Change the clock                                                  | L |

| * | STEP 3 : | Turn on ASSIST-V Trace Facility                                   | Ρ |

| * |          | -                                                                 | G |

| * |          |                                                                   | м |

| * | STEP 4a: | Set protection key to each 2K of memory                           |   |

| * |          |                                                                   | Ι |

| * | 4b:      | Test PCOPSW for S0C5 at the expected address                      | Ρ |

| * |          | IF (not SOC5    not at expected location)                         | L |

| * |          | force 'quick stop'                                                | Ρ |

| * |          | OTHERWISE,                                                        | G |

| * |          | obtain the highest available machine byte and store it in CVTMZ00 | м |

| * |          |                                                                   | Ι |

| * | STEP 4c: | Print CVTMZ00 value                                               | Ρ |

| * |          |                                                                   | L |

| * |          |                                                                   | Ρ |

| * | STEP 5 : | Chain CB100 blocks                                                | G |

| * |          |                                                                   | м |

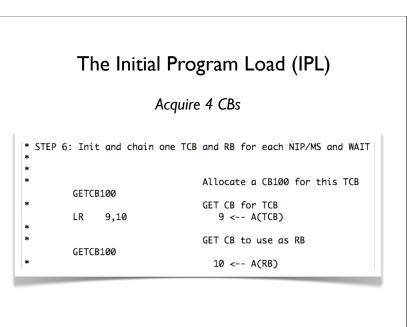

| * | STEP 6 : | Init and chain one TCB and RB for each                            |   |

| * |          | NIP/MS and WAIT                                                   | I |

| * | STED 7 · | Transfer control to dispatcher                                    | P |

9

# The Initial Program Load (IPL)

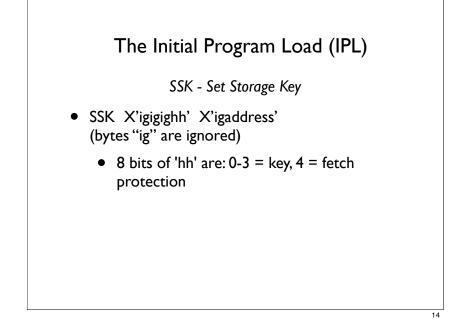

#### Set Storage Key on all Blocks of Memory

| *             | SR   | 2,2              |          | A(lowest storage addr) aka F'0<br>otect key into rightmost byte |

|---------------|------|------------------|----------|-----------------------------------------------------------------|

|               | SSK  | 2,2              | set prot | ection byte of 0(,R2) to X'00                                   |

|               | XOPC | 4                | turn off | f trace for now                                                 |

|               | В    | POINTHER         | jump int | to the loop                                                     |

| IPL00P        | SSK  | 2,2              | prote    | ection byte next block to X'00                                  |

| POINTHER      | LA   | 2,X'800'(,2)     | point    | R2 to next 2K block                                             |

|               | В    | IPLOOP           | repea    | at for all available memory                                     |

| *             |      |                  |          |                                                                 |

| *             |      |                  | NOTE :   |                                                                 |

| •             |      |                  | The loo  | op 'terminates' as a program                                    |

| +             |      |                  | check i  | interrupt (SOC5), at which                                      |

| *             |      |                  | point t  | the PCNPSW will BR to AFTERLOP                                  |

| AFTERLOP<br>* | MVC  | PCNPSW+5(3),ADPC | FLIH+1   | SET instruction address of<br>PSNPSW to the appropriate         |

| *             |      |                  |          | 1st level interrupt handler                                     |

|               | XOPC | 2                | turn tr  | ace back on                                                     |

|             | et nigne           | SL AVC    | ailable Machine Byte                 |

|-------------|--------------------|-----------|--------------------------------------|

| +           |                    |           | ,                                    |

| * SIEP 40   | : Test old PS      | N for SOC | C5 at the expected address           |

| *           |                    |           | at expected location)                |

| *           | OTHERWISE.         | uick stop | )'                                   |

| *           |                    | ha hichor | st available machine byte and        |

| *           |                    | in CVTMZ  |                                      |

| *           |                    |           |                                      |

|             | CLI PCOPSW+        |           | Test PCOPSW for S0C5                 |

|             | BNE IPL0119        |           | If not, force quick stop             |

| •           | LA 3,POINT         |           | GET A(POINTHER)                      |

|             |                    | PCOPSW+5  |                                      |

|             | BNE IPL0119        |           | If interrupt was not at SSK instr.   |

| *           |                    |           | force quick stop                     |

| *           |                    |           | SUCCESS? Finish Step 4b              |

| -           |                    |           | get highest available machine byt    |

| *           | BCTR 2.0           |           |                                      |

| *           | BCTR 2,0           |           | get ingliest available inachtile byt |

| *           | BCTR 2,0<br>L 3,76 |           | Get addressability of CVT            |

| *<br>*<br>* |                    |           |                                      |

| *<br>*<br>* | L 3,76             |           | Get addressability of CVT            |

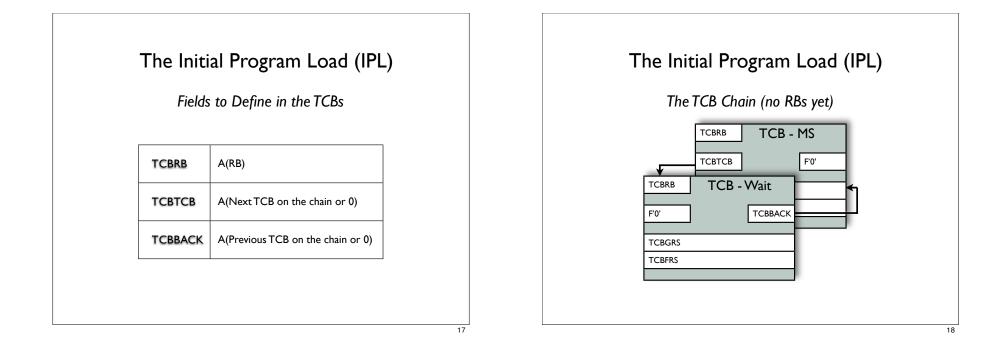

# The Initial Program Load (IPL)

Fields to Define in the RBs

| RBFLGS3 | bit 0 set to 1 for a PRB<br>bit 0 set to 0 for an SVRB                                                        |

|---------|---------------------------------------------------------------------------------------------------------------|

| RBOPSW  | X'FF0401190F',AL3(MS) for MS RB<br>X'FFE601190F',AL3(LEVELABN) for WAIT RB                                    |

| Rblink  | Byte 0 is RBWCF and it must be zero<br>Bytes 1-3 are address portion:<br>for a PRB, this will be the AL3(TCB) |

# The Initial Program Load (IPL)

#### Fields to Define in the CVT (MYCVT)

| A('TCB-Words')  | DSECT = IEATCBP                                                                      |

|-----------------|--------------------------------------------------------------------------------------|

| IEATCBP+4       | (set by Dispatcher)                                                                  |

| A(SVCTABLE)     |                                                                                      |

| A(IST TCB IN CH | AIN) (set by IPL)                                                                    |

| A(CB100HDR)     | Header Address for CB100 CBs                                                         |

| A(Dispatcher)   |                                                                                      |

| SVC 3           | An instruction (!)                                                                   |

| BCR 15,14       | An instruction (!)                                                                   |

|                 | IEATCBP+4<br>A(SVCTABLE)<br>A(IST TCB IN CH<br>A(CB100HDR)<br>A(Dispatcher)<br>SVC 3 |

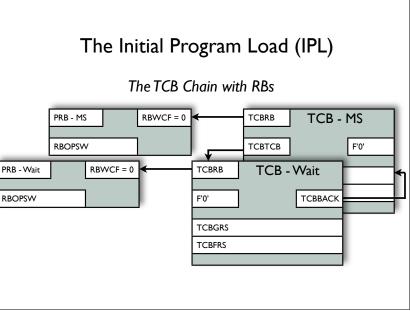

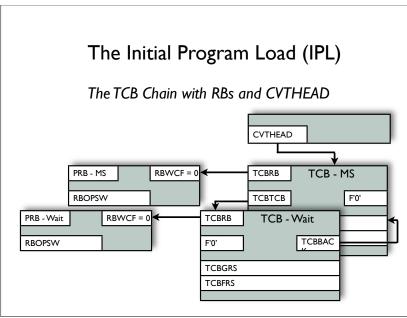

#### The Initial Program Load (IPL)

Fields to Define in the CVT (MYCVT)

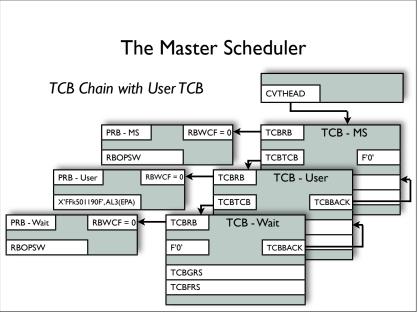

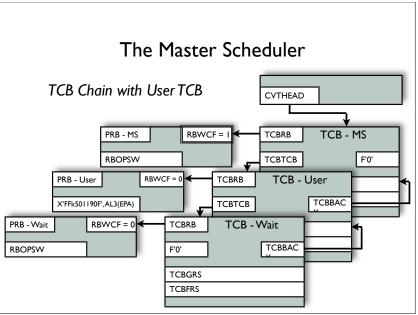

- Build TCB chain for Dispatching

- Point CVTHEAD to MS-TCB

- Chain TCBs

- Down from MS-TCB via TCBTCB (lowest TCBTCB = 0)

- Up from Wait-TCB via TCBBACK (highest TCBBACK = 0)

|        | IF    | PL Basics Have     | e Been Accomplished                 |

|--------|-------|--------------------|-------------------------------------|

| STEP 7 | : Set | to system mode and | d transfer control to dispatcher    |

|        | IC    | 11, IPLUCBKE       | Get Key and Fetch Protect Byte      |

|        |       | 8,X'800'           | Get A(region_                       |

|        | SSK   |                    | Set protection byte for 2K          |

|        |       | ,-                 |                                     |

|        | MVI   | LEVELFLG,C'S'      | Indicate system mode                |

|        |       | TYP1FLAG,C'0'      | Set Type 1 to zero                  |

|        | MVI   | IPLPSW+1,25        | Put 'safety net' (X'0119') at A(0)  |

|        |       |                    |                                     |

|        | DROP  | 12                 | END base R12 range                  |

|        | L     | 12,CVTØDS          | Load address of dispatcher from CVT |

|        | BR    | 12                 | Transfer control to DISPATCHer      |

|        | DROP  | 3                  | END CVT addressability              |

21

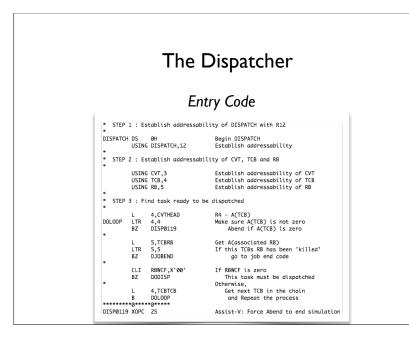

#### The Dispatcher

**Basic Functions**

- Enter Dispatcher with

- R12 A(beginning of Dispatcher)

- R3 A(MYCVT)

### The Dispatcher

#### **Basic Functions**

- Dispatcher 'runs' down the chain of TCBs searching each TCB for:

- I. Non-zero A(TCB) If A(TCB) == 0, then abend

- 2. Non-zero A(RB) in TCB If A(RB) == 0, do Job End Code

- 3. If RBWCF == 0, Do Dispatch!

|                       |             | The Di                                                  | ispatcher                           |

|-----------------------|-------------|---------------------------------------------------------|-------------------------------------|

|                       |             | Dispate                                                 | ch Code                             |

| DODISP<br>*<br>*<br>* | DS<br>At th | 0H<br>is point R3 - A(CVT)<br>R4 - A(TCB)<br>R5 - A(RB) | Perform the Dispatching             |

| *                     | L           | 3,0(0,3)                                                | R3 now points to TCBWORDS           |

|                       | ST          | 4,4(0,3)                                                | Store A(TCB) into TCBWORDS+4        |

| *                     | LD          | 0,TCBFRS                                                | Load all                            |

|                       | LD          | 2,TCBFRS+8                                              | floating point                      |

|                       | LD          | 4,TCBFRS+16                                             | registers from                      |

|                       | LD          | 6,TCBFRS+24                                             | TCBFRS                              |

| •                     | MVC         | LOWPSW(8),RBOPSW                                        | Move PSW of this task into low core |

|                       | MVC         | TCBTDISP(4),TIMER                                       | Store time of Dispatcher in TCB     |

|                       | LM          | 0,15,TCBGRS                                             | Load all GPRs from TCBGRS           |

|                       | LPSW        | LOWPSW                                                  | and Dispatch this task              |

25

#### The Dispatcher

Job End Code

- Not until we introduce SVC 3 in Part 3

- Why?

- Our objective is to get a user's job running

- Thus we require SVCs I & 8 within the Master Scheduler

- First we discuss SVC-FLIH in greater detail

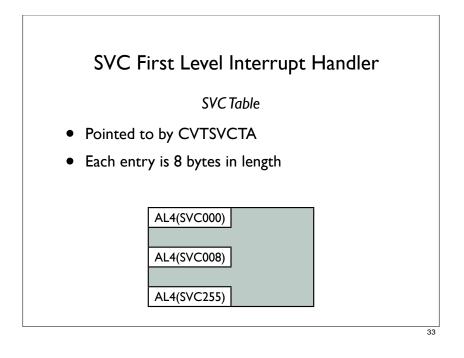

### SVC First Level Interrupt Handler

Role of the First Level Interrupt Handler

- Duties

- I. Save the Essence of the Interrupted Program

- 2. Direct execution to appropriate module

- 3. Direct execution to code to restore Program from Essence

#### SVC First Level Interrupt Handler

Register Convention of SVC FLIHs

| R3  | A(MYCVT)                                             |

|-----|------------------------------------------------------|

| R4  | A(TCB)                                               |

| R5  | A(RB)                                                |

| R6  | A(SVC Routine/Module)                                |

| RI2 | Base register, if needed<br>A(dispatcher) for return |

#### SVC First Level Interrupt Handler

Register Convention of SVC FLIHs

- GPRs 13, 15, 0, 1 Input Parameter registers

- GPRs 15, 0, 1 Output/Return Parameter registers

- SVC Routines may use (store into) the area designated by GPR13, but they will not modify GPR13

29

|   | 510                  |                                | nterrupt Handler                                                                         |

|---|----------------------|--------------------------------|------------------------------------------------------------------------------------------|

|   |                      | The C                          | ode                                                                                      |

| * | L<br>LH<br>SLL<br>LA | 8,3                            | Get A(SVC Table)<br>Get SVC Number from old PSW<br>Multiply by 8<br>Point to table entry |

| * | L<br>BALR            | 6,0(,8)<br>14,6                | Get A(module): SVC Table<br>to module, return on R14                                     |

| * | ST<br>STM            | 15,TCBGRS+(15*4)<br>0,1,TCBGRS |                                                                                          |

|   | L<br>BR              | 12,CVTØDS<br>12                | Get A(dispatcher)<br>Go to Dispatcher                                                    |

SVC First Level Interrupt Handler

SVC I (Wait)

- Input Parameters:

- R0 Number of events

- RI A(Event Control Block)

- SVC I may increment RBWCF in RB of the issuing program

- SVC I with SVC 2 uses ECB to control the 'running' of a program

### SVC First Level Interrupt Handler

SVC I (Wait)

- Suffice it to say:

- Issue SVC I when bit I of the ECB is '0' (the issuing program STOPs!)

- Issue SVC I when bit I of the ECB is 'I' (the issuing program keeps running)

### SVC First Level Interrupt Handler

SVC 8 (Loader)

- Input Parameters:

- R0 Load Address

- RI Available Memory

### SVC First Level Interrupt Handler

SVC 8 (Loader)

- Output Parameters:

- R0 Entry Point Address (EPA) of executable load module

- RI Actual size of loaded program

- RI5 Return Code Typical: 0 = OK 4, 8, ... = Not OK

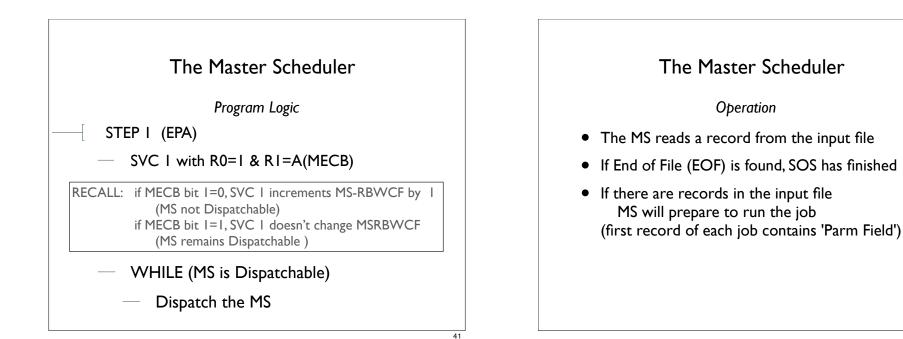

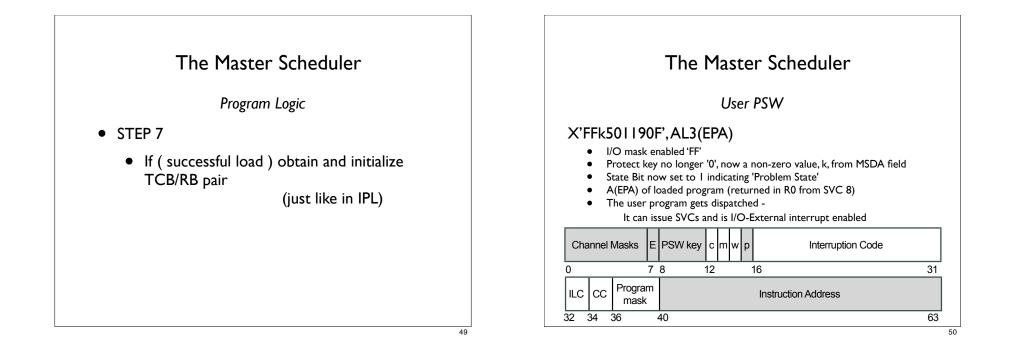

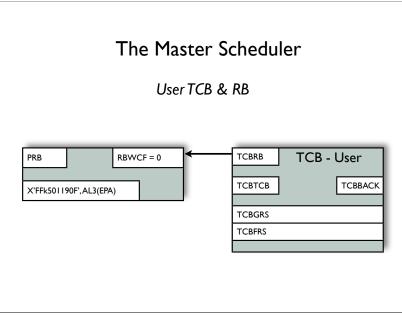

The Master Scheduler

Entry into MS

- Recall:

- IPL branches into Dispatcher

- Dispatcher 'dispatches' (LPSW) MSTCB/ RB to begin execution of Master Scheduler at MS-EPA

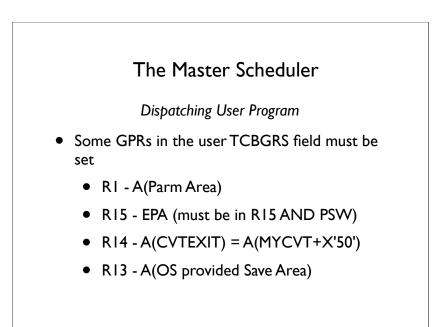

#### The Master Scheduler

Program Logic

- STEP 0

- Assemble Master Scheduler Resident Data Area (MSDA)

- A(first 4K user program region)

- SSK Byte

- Pad Byte

- Set MS-ECB (MECB) to X'7F',C'ECB'

37

The Master Scheduler

Program Logic

- STEP 2 & STEP 3

- pad (MVCL) 4K region with pad byte

- issue SSKs to set protect key for two 2K portions of region

#### The Master Scheduler

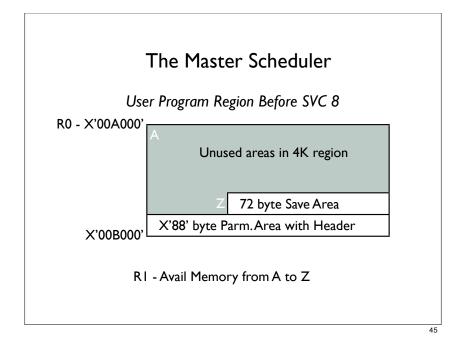

Program Logic

- STEP 4 & STEP 5

- move 'Parm Field' into a Parm Area at highest location in the 4K region

- establish next lower 72 bytes as 18 fullword save area for the user

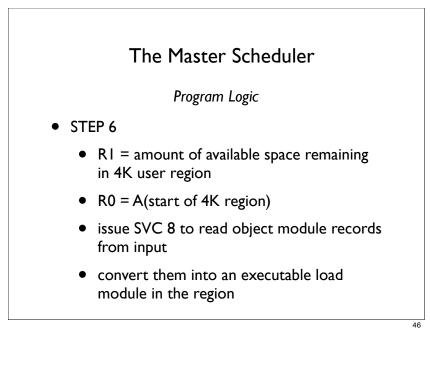

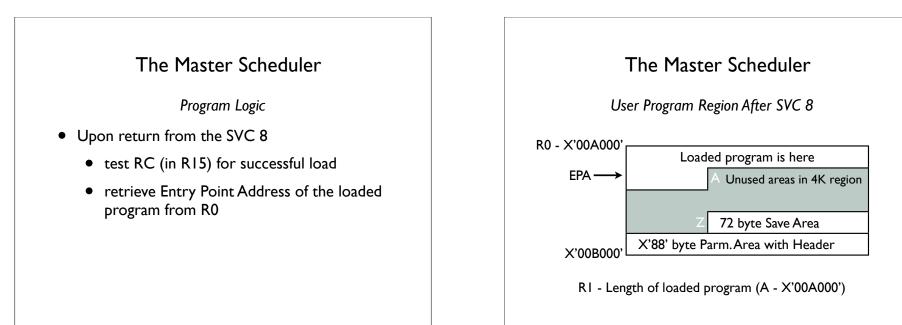

#### The Master Scheduler

Program Logic (Continued)

- STEP 8

- [SOS] generate job start message

- Assist-V XPRNT now, SVC 0 later

- STEP 9

- update fields in MSDA for future jobs

- increment the CUrent numbeR of Initiators (CURI)

#### Program Logic (Continued)

- STEP IO

- Chain user TCB just after MS-TCB

- STEP ||

- Not until we get to multiprogramming

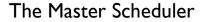

#### Dispatching User Program

- With three TCBs in the chain, Dispatcher picks first one: MS-TCB

- To dispatch User-TCB, MS-TCB must be made non-dispatchable

- To do this:

- Set MECB to 0

- Issue SVC I against MECB

53

#### The Master Scheduler

Program Logic (Continued)

- STEP 12 (bottom of MS Loop)

- set MECB to 0 (XC)

- branch to SVC I instruction at top of MS Loop

#### Dispatching User Program

- Issuing SVC I with zero MECB makes MS-TCB non-dispatchable

- SVC 1 increments RBWCF (MS RB now waiting on 1 task)

- With MS-TCB non-dispatchable dispatcher now picks User-TCB

57

### **Sneak Preview**

Part 3: SVCs and More SVCs

- SVC Types: Enabled or Disabled

- Scheduling and Dispatching the SVRB

- SVC 3 RB 'Killer'

- The 'valve' (SVC I & SVC 2)

- SVC 8 Loader

- SVC 13 ABEND

| Questions                                                          |    |

|--------------------------------------------------------------------|----|

| rrannie@cs.niu.edu<br>m-kozomara@ti.com<br>www.cs.niu.edu/~rrannie |    |

|                                                                    | 62 |